Hix, nói vậy thì mình chạy song mã, tốt nhất là cứ 2 chú step có encoder cho nó khỏe?

Hix, nói vậy thì mình chạy song mã, tốt nhất là cứ 2 chú step có encoder cho nó khỏe?

quá rắc rối đó là lí do em mới dừng lại ở anpha step , về cơ khí em không lo em chỉ lo đi kèm theo em nó quá khó nhai , thế là vứt xó 3 em servo 400W

Nguyễn Hoàng Nam

n_h_n2002@yahoo.com DT: 0908415648

Đa số các động cơ servo thường turning sẵn ở các mức chuẩn cho thuận tiện trong việc sử dụng. Ví dụ Mitsu dòng MR-C là 5 mức, Yaskawa là 12 mức, không nên chỉ dựa vào đó mà cài đặt cho máy, mà phải dựa trên quá trình tính toán dựa trên các thông số của cơ hệ cụ thể.

Nếu cơ hệ có quán tính lớn mà cài đặt thông số nhỏ thì động cơ sẽ "yếu" và ngược lại.

Còn về việc sai lệch của servo thì có thể giải thích nôm na như sau:

Giả sử drop pulse cài đặt là 200 ( nghĩa là cho phép sai lệch =< 200 xung encoder tại vị trí kết thúc lệnh). TÍnh trung bình servo sai lệch 1 xung/1 cặp lệnh ( CW và CCW) thì sau 1. 10^6 lệnh thì sai lệch sẽ là 1 triệu xung encoder. Giả sử encoder có 4000ppr, vitme bước 10 thì sai lệch tích lũy sẽ là (1.10^6/4000)/10) =mm. hơi say nên ko biết gõ có sai ko. Hic

Vì vậy phải chọn servo có công suất đủ lớn để giảm thiểu drop pulse, response time, overshot và undershot

Còn nữa, giả thiết khoảng death time của hai chuỗi xung liên tiếp trong Mach3 là 100us, nếu servo cài đặt response time >100us thì servo chưa đạt đến vị trí yêu cầu thì phải thực hiện lệnh kế tiếp gây nên sai số. Muốn khắc phục thì có 2 cách, hoặc là giảm tốc độ hoặc giảm response time.

Lần sửa cuối bởi Tuanlm, ngày 01-01-2015 lúc 09:20:46 PM.

em đã tìm mua được sợi cáp( có mỗi sợi dây nó quất em 1 củ), nghiên cứu manual em cũng k ngán, nghe các bác phân tích máu quá, mai bật sigmawin+ ra chiến đấu với bộ thông số thử xem thế nào

aplicationote servo drive với tms320f28035

harware+code

https://drive.google.com/folderview?...28&usp=sharing

Lưu ý, cái này dùng resolver.

phần công suất, IPM của fairchild em thấy là giá cạnh tranh nhất

vài hd của hãng vể IPM

https://www.fairchildsemi.com/refere...gns/RD-344.pdf

https://www.fairchildsemi.com/collat...sign-Guide.pdf

Một vài trở ngại lớn về kiến thức nên mình chắc phải hủy bỏ ý tưởng ac servo. Thêm nữa mcu Pic dễ bị nhiễu bởi các nguyên nhân ko kiểm soát. Các cao thủ làm ơn trợ giúp công lực.

Lần sửa cuối bởi nhatson, ngày 05-01-2015 lúc 07:49:20 AM.

Ủa, bác Tuanlm làm được AC Servo driver rồi mà?

Lần sửa cuối bởi Gamo, ngày 05-01-2015 lúc 09:00:28 AM.

Haha!

Cao thủ về mảng này còn đầy... chỉ là đang ẩn mình chờ cơ hội bác ơi. Mà trong đó dân ngoại đạo cũng nhiều lắm à.

Lúc trước em hay chém là dân cơ khí đi làm điện tử, dân cơ khí đi làm lập trình bla bla.

Từ khi biết bác NS e hết dám ho rồi ạ. Bác NS học làm quảng cáo mà không chịu làm.. chuyển qua làm driver làm chi không biết nữa

Em gnhi là cao thủ ẩn danh còn rất nhiều.

Dùa chút chơi heheh

DT: O7837277II - CKD's Youtube Channel - Facebook - Tổng hợp chủ đề

17 ds 3, Thạnh Mỹ Lợi, Q2, tp.HCM

cao thủ nhiều, nhưng mờ em thấy thường làm việc cho 1 chỗ nào đó, có nhiều ràng buộc , đợi các cụ ấy nghỉ hưu rồi mới viết hồi ký được ah

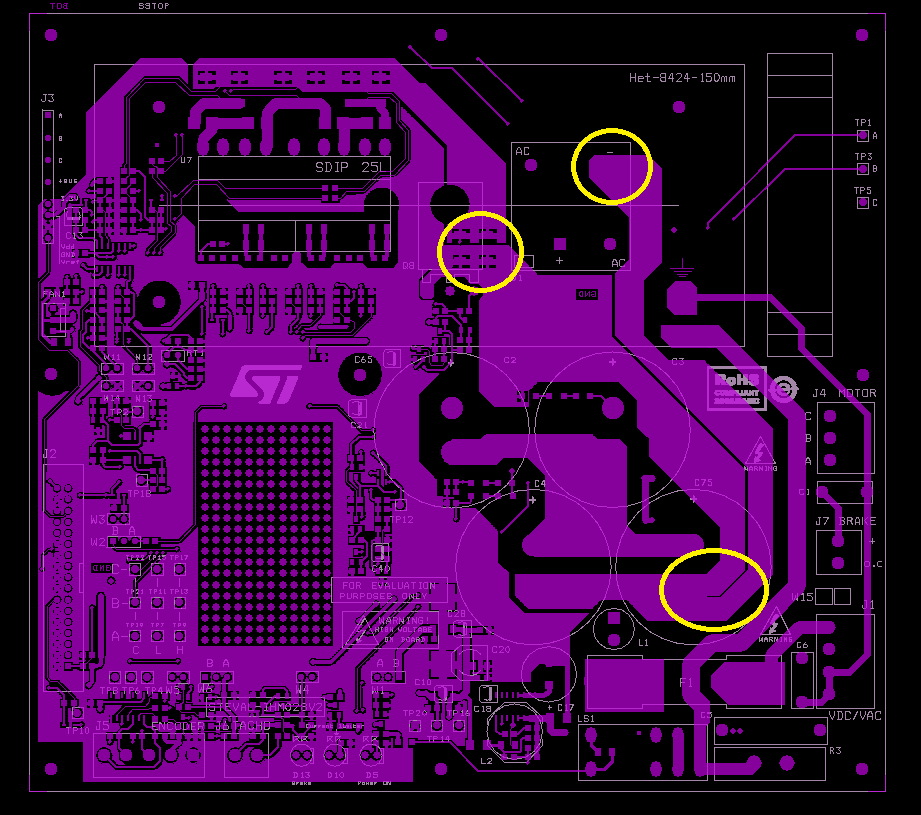

phần công suất mẫu của ST 2000W,

layout > cái này nghề cũ của cụ anhxco thì phải? trước em có thảo luận với cụ về ground loop, như trong bản vẽ, cụ thấy mass ko phủ hết mà nó rẽ nhánh từ cấu diode và tụ nguồn ko?

http://www.st.com/web/en/catalog/tools/PF260361

b.r

Lần sửa cuối bởi nhatson, ngày 05-01-2015 lúc 10:26:25 AM.

Mấy cái vụ chống/giảm nhiễu trong PCB này là một môn khoa học khó nhằn à. Không phải cứ phủ ground từ đầu tới đít là tốt à.

Trong PCB thì không biết nhưng trong công nghiệp thì chia ra 2 hướng giải quyết.

- Cô lập vùng nhiễu.. tức không cho nhiễu thoát ra ngoài ảnh hưởng thiết bị khác. Nhưng nếu không triệt tiêu được nhiễu từ thiết bị chống nhiễu (thường dạng lồng faraday và được tiếp đất) thì chính thiết bị chống nhiễu khi đó lại thành vật truyền dẫn, hoặc anten phát nhiễu. Khi đó thì tình hình càng tồi tệ hơn.

- Bảo vệ phần nhạy cảm. Cái này thì được ứng dụng nhiều hơn. Tập trung bảo vệ trước những thiết bị nhạy cảm với nhiễu. Cách này cũng dễ hơn vì cường độ nhiễu đến thiết bị đã suy giảm trong môi trường.

Nếu kết hợp được cả 2 là tuyệt vời nhất.

Để ý thấy trong PCB chạy tốc độ cao thì mọi yếu tố đều thấy ảnh hưởng lớn -> nghiêm trọng

- Điện dung giữa các đường mạch, layout đều ảnh hưởng.

- Độ dài đường mạch, kích thước, điện trở...

- Hình dạng khúc khủy, thẳng v.v...

Máy cái này thì em chém thôi.. không có kinh nghiệm gì hết

DT: O7837277II - CKD's Youtube Channel - Facebook - Tổng hợp chủ đề

17 ds 3, Thạnh Mỹ Lợi, Q2, tp.HCM

Lần sửa cuối bởi nhatson, ngày 05-01-2015 lúc 10:44:46 AM.

1 điển hình các tài liệu hãng cũng cỏ giá trị tham khảo thôi

steval-ihm028V1 và steval-ihm028v2 , tài liệu bị sai

V1

http://www.st.com/web/catalog/tools/...C1077/PF251251

V2

http://www.st.com/web/en/catalog/tools/PF260361

Lần sửa cuối bởi nhatson, ngày 05-01-2015 lúc 10:57:56 AM.

Hi bác NS và bác CKD!

Em không chuyên PCB ạ, trước làm thời gian rồi chuyển qua system, chủ yếu và sche và signal , thêm mấy thứ vớ vẫn,( nhưng cũng chuyên và digital thui) và giờ thì giải nghệ cũng 1 thời gian rồi.

Cái e nói là chung thôi bác NS ạ, còn tùy vào trường hợp cụ thể như bác CKD nói, và e vẫn khẳng định là phủ mass là cách tối ưu để giảm nhiễu nhưng phải phủ đúng cách à. Xem qua PCB bác NS để ý nó không phải không phủ mà phủ ở nơi cần ( vùng signal) và lấy mass sau khi lọc để phủ bác ạ.

Về high speed mà bác CKD đề cập thì ngoài việc giảm noise còn yếu tố cực kỳ quan trọng là phối hợp trở kháng và đồng bộ, lúc này yêu cầu phải tính toán chiều dài, bề rộng- khoảng cách trace cũng như khoảng cách các layer, vật liệu .v.v.

Về cơ bản layout để giảm noise thì ai làm layout nhiều, có nhiều kinh nghiệm thì sẽ làm tốt vì thực sự cái này không liên quan nhiều đến tính toán( từ việc layout plane, signal đến việc place part), chỉ cái phần high speed kia là bắt buộc thôi à.

Và cuối cùng, lý thuyết thế nào cũng phải kiểm chứng, vì sản phẩm là sản phẩm thật chứ không nằm trên thiết kếnữâ lý thuyết thế nào cũng phải kiểm chứng, vì sản phẩm là sản phẩm thật chứ không nằm trên thiết kế nữa. Như bác NS nói(cái này luôn đúng), các bác cần có dụng cụ để test, còn không thì cứ chạy bằng niềm tin và hy vọng

PS: Nếu bác NS làm layout 4 lớp cũng nên tính đến chuyện này, không tính thì nó hơi phí cái khoản 4 lớp bác ạ.

Vài dòng chia sẽ. Nếu mà có giúp gì đc cho các bác nghiên cứu thì hú e, sẵn sàng giúp các bác hết sức ( chỉ sợ sức không đủ thui))

Lần sửa cuối bởi anhxco, ngày 05-01-2015 lúc 11:10:28 AM.

em ko đề cập tới mass signal,

vấn đề em muốn đề cập là tại sao ko phủ thẳng mass từ chân GND của diode mà tách ra 2 đường đến chân GND của tụ đấy ah

quan điểm của em, nếu phủ thẳng nó sẽ dẫn tới mass của công suất và mass tụ ( mấy cái này dòng lớn ) nó trở về chân GND ko đồng đều > gound loop > cụ ko công nhận cái này

trong tài liệu hd của fairchild có ghi, và cụ ko đồng tình về việc này, nên em dẫn chứng cho cụ xem, em cũng chắc chắn nếu phủ , ko tách ra 2 đường sẽ có GND noise tệ hơn là tách ra

Lần sửa cuối bởi nhatson, ngày 05-01-2015 lúc 11:19:13 AM.

Hì, cái nì e nói rồi, cần phủ mass sạch, nguyên tắc với nguồn, cụ cần place tụ lọc càng gần nguồn vào càng tốt, việc layout ở trên e thây hơi xa, vì vậy nó lấy mass bắt đầu từ tụ ra. nếu cụ lấy luôn từ chân diod thì không đảm bảo đc nguồn đã sạch. còn việc ground loop nói thật trước giờ e không quan tâm, trước giờ e làm board ít nhất là 4 lớp ( mà rất ít), còn lại tầm 8 lớp trở lên, lúc này có lớp plane ở giữa, cụ cứ vô tư dùng stitching via, đảm bảo giảm nhiễu tối đa. Còn nói thật cụ analog thì e chịu, không phải chuyên môn của e, nhưng cơ bản nó đều theo 1 nguyên tắc cả.

Lần sửa cuối bởi anhxco, ngày 05-01-2015 lúc 11:23:59 AM.